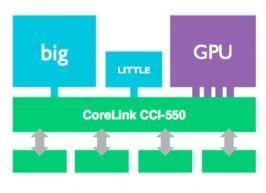

日前,ARM宣布推出两套新的强化版Corelink系统IP,一个是CoreLink CCI-550互联总线,用于big.LITTLE多核心架构、完全一致性GPU,而且延迟更低、吞吐量更高,另一个则是CoreLink DMC-500内存控制器,带宽更高、延迟更低。ARM此举为将来的异构系统芯片奠定了基础。

据ARM称,CCI-550和今年二月份随同Cortex-A72 CPU核心诞生的CCI-500一样,都是目前高通、联发科普遍使用的CCI-400的换代产品,最大变化就是加入嗅探过滤器(snoop filter),取代第一代大小核架构里的广播式设计,同时与所有核心、缓存通信,因而延迟更低、扩展性更强、功耗更低(节省最多上百毫瓦)、性能更高。SoC设计师可以配置存储器通道数量、跟踪器尺寸、嗅探过滤器过滤能力及6个处理器群。

CCI-400只能支持两个CPU簇(cluster),CCI-500翻番到四个,全新CCI-550则不但可以互连六个CPU簇,还支持完全一致性的CPU/GPU混合互连,而且增加了读取数据缓冲,嗅探数据带宽也翻了一番,系统带宽可超过50GB/s。CCI-550还支持最多六个内存通道(32-48位物理寻址)、三个系统主界面、六个ACE主端口。该技术适用于手机和数字电视的4K成像以及汽车和网络应用,整颗处理器可以做到24核心。

CoreLink DMC-500是DMC-400的升级版本,可支持LPDDR4/3与最高LPDDR4-4267存储规格。在整体设计层面,CoreLink CCI-550和CoreLink DMC-500可共同协作实现超过50GB/s的系统存储器峰值带宽,可应用于平板电脑和智能手机的4K视频。

The Linley Group高级分析师Mike Demle表示:“如果想要为客户提供先进的功能,如4K视频的录制和播放、120fps的摄像头、4K高清显示器等,那么就必定需要将异构的CPU、GPU和加速器放在同一个高速缓存系统里同步工作,并且还必须要严格控制好功耗。”

CoreLink CCI-550、CoreLink DMC-500相关产品已经交给主要合作伙伴,预计在2016年下半年间问世,在新工艺下频率都能超过1GHz。

-

shawarma 最新版 1.0.30 84.73 MB

下载

小编推荐

视频推荐

更多 手游风云榜

更多 资讯阅读

更多 -

- 《热血江湖手游技能加点攻略》(掌握技能加点要诀,成就无敌江湖之王)

- 业内资讯 2025-05-21

-

- 新版本赏金玩法出装攻略(全面解析最优出装方案,让你在新版本赏金玩法中独领风骚)

- 业内资讯 2025-05-20

-

- 老鼠铲子出装铭文攻略(打造无敌老鼠!)

- 业内资讯 2025-05-20

-

- 王者太虚战场出装攻略(打造最强装备,征服太虚战场)

- 业内资讯 2025-05-19

-

- 制裁战神队友出装攻略(打造最强战队,击败敌人无往不胜)

- 业内资讯 2025-05-19

-

- 《狐狸端游联盟出装攻略》(狐狸出装攻略,助你战胜对手!)

- 业内资讯 2025-05-18

-

- 王者荣耀(揭开哪吒输出利器,带你稳定carry全场)

- 业内资讯 2025-05-18

-

- 地狱男爵技能加点攻略

- 业内资讯 2025-05-16

-

- 逐梦三国(揭秘孙权如何在起凡中成为绝对强者)

- 业内资讯 2025-05-16

-

- 《凯德出装铭文推荐攻略,助你稳定击败对手》

- 业内资讯 2025-05-13

-

- 护卫乌龟出装攻略(如何选择适合乌龟的护卫出装)

- 业内资讯 2025-05-11

-

- 《公主级2-6攻略技能大揭秘》(掌握攻略技能,成为公主级2-6的王者!)

- 业内资讯 2025-05-08